# FUNDAMENTALS OF DIGITAL &LECTRONICS

# **Authors**

- Dr. Santhosh Kumar Allemki

- Dr. Shatrughna Prasad Yadav

- Dr. Vijayasaro Vijayaregunathan

- Dr. Gambala Kiranmaye

# Fundamentals of Digital Electronics

# By

Dr. Santhosh Kumar Allemki

Dr. Shatrughna Prasad Yadav

Dr. Vijayasaro Vijayaregunathan

Dr. G Kiranmaye

# TABLE OF CONTENTS

# **CHAPTER 1 NUMBER SYSTEM**

| 1.1 Review of Number Systems                  | 1  |

|-----------------------------------------------|----|

| 1.1.1 Decimal system                          | 2  |

| 1.1.2 Binary System                           | 2  |

| 1.1.3 Octal System                            | 3  |

| 1.1.4 Hexadecimal System                      | 3  |

| 1.2 Code Conversion                           | 3  |

| 1.3 1's and 2's complement                    | 6  |

| 1.4 Arithmetic Operations                     | 7  |

| 1.5 Binary Codes                              | 8  |

| 1.6 Code Converters                           | 11 |

| CHAPTER 2 BOOLEAN ALGEBRA                     | 31 |

| 2.1 Fundamental postulates of Boolean algebra | 31 |

| 2.2 Basic Theorems                            | 32 |

| 2.3 Properties of Boolean algebra             | 33 |

| 2.4 Boolean Functions                         | 35 |

| 2.5 Complement of A Function                  | 36 |

| 2.6 Logic Gates                                          | 37 |

|----------------------------------------------------------|----|

| 2.6.1 Basic Logic Gates                                  | 37 |

| 2.6.2 UNIVERSAL GATES                                    | 38 |

| 2.7 Canonical and Standard Forms                         | 43 |

| CHAPTER 3 KARNAUGH MAP MINIMIZATION                      | 47 |

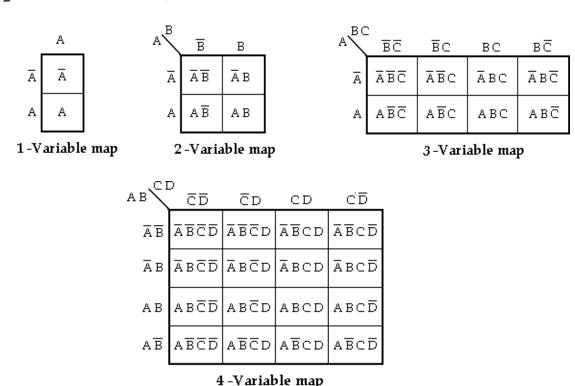

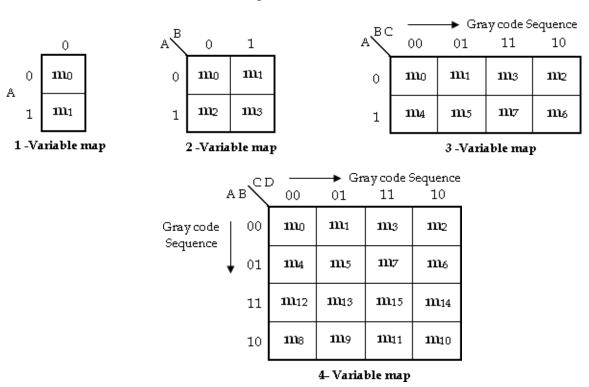

| 3.1 Two- Variable, Three Variable and Four Variable Maps | 47 |

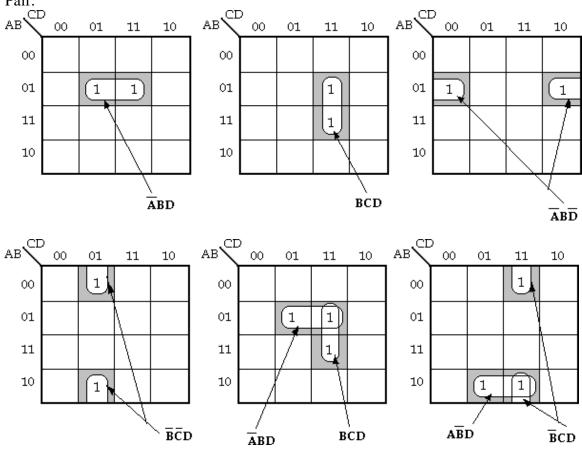

| 3.2 Grouping cells for Simplification                    | 49 |

| 3.3 Don't care Conditions                                | 57 |

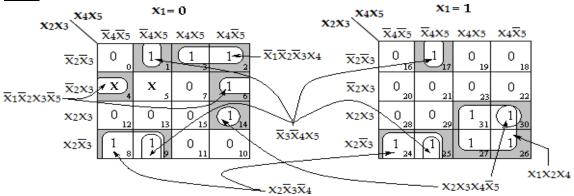

| 3.4 Five- Variable Maps:                                 | 59 |

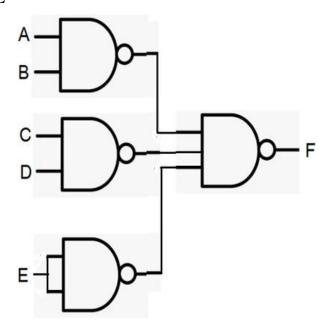

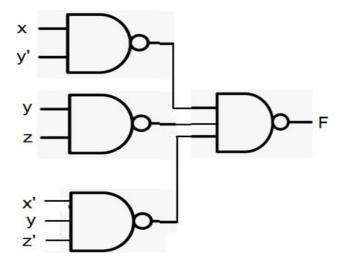

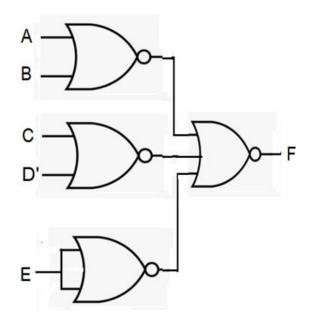

| 3.5 Two Level Gate Network                               | 62 |

| CHAPTER 4 COMBINATIONAL CIRCUITS                         | 65 |

| 4.1 Introduction                                         | 65 |

| 4.2 Design Procedure                                     | 66 |

| 4.3 Arithmetic Circuits – Basic Building Blocks          | 66 |

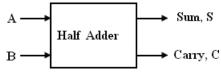

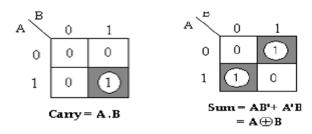

| 4.3.1 Half-Adder                                         | 66 |

| 4.3.2 Full-Adder                                         | 67 |

| 4.3.3 Half -Subtractor                                   | 70 |

| 4.3.4 Full Subtractor                                    | 71 |

| 4.4 Binary Adder (Parallel Adder):                       | 74 |

| 4.5 Carry Propagation–Look-Ahead Carry Generator | 75 |

|--------------------------------------------------|----|

| 4.6 Binary Subtractor (Parallel Subtractor)      | 77 |

| 4.7 Parallel Adder/ Subtractor                   | 78 |

| 4.8 Decimal Adder (BCD Adder):                   | 79 |

| 4.9 Magnitude Comparator                         | 81 |

| 4.10 Decoder                                     | 83 |

| 4.11 Encoders                                    | 86 |

| 4.12 Multiplexer                                 | 90 |

| 4.13 Demultiplexer                               | 95 |

# CHAPTER 1 NUMBER SYSTEM

# 1.1Review of Number Systems:

Many number systems are in use in digital technology. The most common are the decimal, binary, octal, and hexadecimal systems. The decimal system is clearly the most familiar to us because it is tools that we use every day.

Types of Number Systems are

- Decimal Number system

- Binary Number system

- Octal Number system

- Hexadecimal Number system

Table 1.1 Types of Number Systems

| DECIMAL | BINARY | OCTAL | HEXADECIMAL |

|---------|--------|-------|-------------|

| 0       | 0000   | 0     | 0           |

| 1       | 0001   | 1     | 1           |

| 2       | 0010   | 2     | 2           |

| 3       | 0011   | 3     | 3           |

| 4       | 0100   | 4     | 4           |

| 5       | 0101   | 5     | 5           |

| 6       | 0110   | 6     | 6           |

| 7       | 0111   | 7     | 7           |

| 8       | 1000   | 10    | 8           |

| 9       | 1001   | 11    | 9           |

| 10      | 1010   | 12    | A           |

| 11      | 1011   | 13    | В           |

| 12      | 1100   | 14    | С           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | Е           |

| 15      | 1111   | 17    | F           |

Table 1.2 Number system and their Base value

| System       | Base | Digits           |

|--------------|------|------------------|

| Binary       | 2    | 0 1              |

| Octal        | 8    | 01234567         |

| Decimal      | 10   | 0123456789       |

| Hexa Decimal | 16   | 0123456789ABCDEF |

#### 1.1.1 Decimal system:

Decimal system is composed of 10 numerals or symbols. These 10 symbols are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Using these symbols as digits of a number, we can express any quantity. The decimal system is also called the base-10 system because it has 10 digits. Even though the decimal system has only 10 symbols, any number of any magnitude can be expressed by using our system of positional weighting.

| 103                          | 102  | 10 <sup>1</sup> | 100 |               | 10-1 | 10-2  | 10-3                          |

|------------------------------|------|-----------------|-----|---------------|------|-------|-------------------------------|

| =1000                        | =100 | =10             | =1  | ٠             | =0.1 | =0.01 | =0.001                        |

| Most<br>Significant<br>Digit |      |                 |     | Decimal point |      |       | Least<br>Significant<br>Digit |

**Example:** 3.1410, 5210,102410

#### 1.1.2 Binary System:

In the binary system, there are only two symbols or possible digit values, 0 and 1. This base-2 system can be used to represent any quantity that can be represented in decimal or other base system.

| 23                           | 22 | 21 | 20 |              | 2-1  | 2-2   | 2-3                           |

|------------------------------|----|----|----|--------------|------|-------|-------------------------------|

| =8                           | =4 | =2 | =1 | •            | =0.5 | =0.25 | =0.125                        |

| Most<br>Significant<br>Digit |    |    |    | Binary point |      |       | Least<br>Significant<br>Digit |

In digital systems the information that is being processed is usually presented in binary form. Binary quantities can be represented by any device that has only two operating states or possible conditions. E.g.. A switch is only open or closed. We arbitrarily (as we define them) let an open switch represent binary 0 and a closed switch represent binary 1. Thus we can represent any binary number by using series of switches.

Binary 1: Any voltage between 2V to 5V Binary 0: Any voltage between 0V to 0.8V

Not used: Voltage between 0.8V to 2V in 5 Volt CMOS and TTL Logic, this may cause error in a digital circuit. Today's digital circuits works at 1.8 volts, so this statement may not hold

true for all logic circuits.

#### 1.1.3 Octal System:

The octal number system has a base of eight, meaning that it has eightpossible digits: 0,1,2,3,4,5,6,7.

| 83                           | 82  | 82 | 81 | 80             | 8-1  | 8-2   | 8-3                           |

|------------------------------|-----|----|----|----------------|------|-------|-------------------------------|

| =512                         | =64 | =8 | =1 | •              | =1/8 | =1/64 | =1/512                        |

| Most<br>Significant<br>Digit |     |    |    | Octal<br>point |      |       | Least<br>Significant<br>Digit |

#### 1.1.4 Hexadecimal System:

The hexadecimal system uses base 16. Thus, it has 16 possible digit symbols. It uses the digits 0 through 9 plus the letters A, B, C, D, E, and F as the 16 digit symbols.

| 16 <sup>3</sup>              | 16 <sup>2</sup> | 16 <sup>1</sup> | $16^{0}$ |                       | 16 <sup>-1</sup> | 16-2   | 16-3                          |

|------------------------------|-----------------|-----------------|----------|-----------------------|------------------|--------|-------------------------------|

| =4096                        | =256            | =16             | =1       | •                     | =1/16            | =1/256 | =1/4096                       |

| Most<br>Significant<br>Digit |                 |                 |          | Hexadeci<br>mal point |                  |        | Least<br>Significant<br>Digit |

#### 1.2 Code Conversion

Converting from one code form to another code form is called code conversion, like converting from binary to decimal or converting from hexadecimal to decimal.

• **Binary-To-Decimal Conversion:** Any binary number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the binary number which contain a 1.

| Binary                                        | Decimal     |

|-----------------------------------------------|-------------|

| 110112                                        |             |

| $= (1*2^4) + (1*2^3) + 0 + (1*2^1) + (1*2^0)$ | =16+8+0+2+1 |

| Result                                        | 2710        |

#### Decimal to binary Conversion:

There are 2 methods:

- Reverse of Binary-To-Decimal Method

- Repeat Division

# **Reverse of Binary-To-Decimal Method**

| Decimal | Binary                 |

|---------|------------------------|

| 4510    | =32+0+8+4+0+1          |

|         | $=2^5+0+2^3+2^2+0+2^0$ |

| Result  | =1011012               |

# Repeat Division-Convert decimal to binary: This method uses repeated division by 2.

| Division | Remainder             | Binary                    |

|----------|-----------------------|---------------------------|

| 25/2     | = 12+ remainder of 1  | 1 (Least Significant Bit) |

| 12/2     | = 6 + remainder of 0  | 0                         |

| 6/2      | = 3 + remainder of  0 | 0                         |

| 3/2      | = 1 + remainder of 1  | 1                         |

| 1/2      | = 0 + remainder of 1  | 1 (Most Significant Bit)  |

| Result   | 2510                  | = 110012                  |

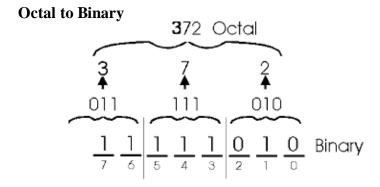

# • Binary-To-Octal / Octal-To-Binary Conversion Binary to octal

$$100\ 111\ 0102 = (100)\ (111)\ (010)2 = 4\ 7\ 28$$

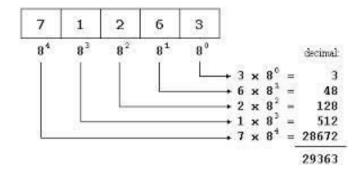

# • Decimal -To-Octal / Octal-To- Decimal Conversion Decimal to octal

| Division | Result               | Binary                    |

|----------|----------------------|---------------------------|

| 177/8    | = 22+ remainder of 1 | 1 (Least Significant Bit) |

| 22/8     | = 2 + remainder of 6 | 6                         |

| 2/8      | = 0 + remainder of 2 | 2 (Most Significant Bit)  |

| Result   | 17710                | = 2618                    |

| Binary   |                      | = 0101100012              |

#### **Octal to Decimal**

#### Hexadecimal to Decimal/Decimal to Hexadecimal Conversion

#### • Decimal to Hexadecimal

| Division | Result                | Hexadecimal                 |

|----------|-----------------------|-----------------------------|

| 378/16   | = 23+ remainder of 10 | A (Least Significant Bit)23 |

| 23/16    | = 1 + remainder of 7  | 7                           |

| 1/16     | = 0 + remainder of 1  | 1 (Most Significant Bit)    |

| Result   | 378 10                | = 17A <sub>16</sub>         |

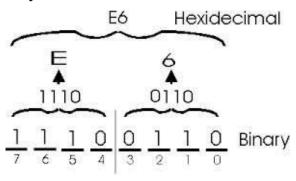

# • Binary-To-Hexadecimal / Hexadecimal-To-Binary Conversion

**Binary-To-Hexadecimal:**  $1011\ 0010\ 11112 = (1011)\ (0010)\ (1111)2 = B\ 2\ F16$

# **Hexadecimal to binary**

#### Octal-To-Hexadecimal Hexadecimal-To-Octal Conversion

- Convert Octal (Hexadecimal) to Binary first.

- Regroup the binary number by three bits per group starting from LSB if Octal is required.

- Regroup the binary number by four bits per group starting from LSB if Hexadecimal is required.

#### Octal to Hexadecimal

| Octal                         | Hexadecimal                             |  |  |  |

|-------------------------------|-----------------------------------------|--|--|--|

| = 2 6 5 0                     |                                         |  |  |  |

| <b>010</b> 110 <b>101</b> 000 | = <b>0101</b> 1010 <b>1000</b> (Binary) |  |  |  |

| Result                        | =(5A8)16                                |  |  |  |

#### Hexadecimal to octal

| Hexadecimal | Octal                                    |

|-------------|------------------------------------------|

| (5A8)16     | = <b>0101</b> 1010 <b>1000</b> (Binary)  |

|             | = <b>010</b> 110 <b>101</b> 000 (Binary) |

| Result      | = 2 6 5 0 (Octal)                        |

#### 1.3 1's and 2's complement

Complements are used in digital computers to simplify the subtraction operation and for logical manipulation. There are TWO types of complements for each base-r system: the radix complement and the diminished radix complement. The first is referred to as the r's complement and the second as the (r - 1)'s complement, when the value of the base r is substituted in the name. The two types are referred to as

The 2's complement and 1's complement for binary numbers and the 10's complement and 9's complement for decimal numbers.

- The 1's complement of a binary number is the number that results when we change all 1's to zeros and the zeros to ones.

- The 2's complement is the binary number that results when we add 1 to the 1's complement. It is used to represent negative numbers.

2's complement=1's complement+1

0 0 1 0 1's complement

# **1.4 Arithmetic Operations**

# **Binary Equivalents**

1 Nybble (or nibble) = 4 bits 1 Byte = 2 nibbles = 8 bits

1 Kilobyte (KB) = 1024 bytes

1 Megabyte (MB) = 1024 kilobytes = 1,048,576 bytes

1 Gigabyte (GB) = 1024 megabytes = 1,073,741,824 bytes

#### **Binary Addition**

Rules of Binary Addition

- 0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 0, and carry 1 to the next more significant bit

Example: 00011010 + 00001100 = 00100110

# **Binary Subtraction**

**Rules of Binary Subtraction**

- 0 0 = 0

- 0 1 = 1, borrow 1 from the next bit

- 1 0 = 1

- 1 1 = 0

# Example:

| 00100101 - 00010001= 00010100 | 0   | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

|-------------------------------|-----|---|---|---|---|---|---|---|

|                               | + 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

|                               | 0   | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

#### **Binary Multiplication**

Rules of Binary Multiplication

- $0 \times 0 = 0$

- $0 \times 1 = 0$

- $1 \times 0 = 0$

- $1 \times 1 = 1$ , and no carry or borrow bits

#### Example

|   | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|---|

| × | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | + |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 |   | + |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

$00101001 \times 00000110 = 11110110$

#### 1.5 Binary Codes

Binary codes are codes which are represented in binary system with modification from the original ones. There are two types of binary codes: Weighted codes and non-weighted codes. BCD and the 2421 code are examples of weighted codes. In a weightedcode, each bit position is assigned a weighting factor in such a way that each digit can be evaluated by adding the weight of all the 1's in the coded combination. Types of Binary Codes are

- Weighted Codes

- Non Weighted Codes

- Reflective Codes

- Sequential Codes

- Error Detecting and Correction Codes

- Alphanumeric Codes

# **Weighted Code**

- 8421 code, Most common, Default

- The corresponding decimal digit is determined by adding the weights associated with the 1s in the code group.  $62310 = 0110\ 0010\ 0011$

• The weights associated with the bits in each code group are given by the name of the code

#### **Non weighted Codes**

- 2421 code: This is a weighted code; its weights are 2, 4, 2 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 2 + 4 + 2 + 1 = 9. Hence the 2421 code represents the decimal numbers from 0 to 9.

- 5211 codes: This is a weighted code; its weights are 5, 2, 1 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 5 + 2 + 1 + 1 = 9. Hence the 5211 code represents the decimal numbers from 0 to 9.

#### Reflective code:

A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

#### **Sequential code:**

A code is said to be sequential when two subsequent codes, seen as numbers in binary representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

• Excess-3 code: Excess-3 is a non weighted code used to express numbers. The code derives its corresponding 8421 code plus 0011(3).

**Example:** 1000 of 8421 = 1011 in Excess-3

#### Gray code:

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next. The Gray code is non-weighted code, as the position of bit does not contain any weight. In digital Gray code has got a special place. The gray code is a reflective digital code which has the special property that any twosubsequent numbers codes differ by only one bit. This is also called a unit-distance code. Important when an analog quantity must be converted to a digital representation. Only one-bit changes between two successive integers which are being coded.

| Decimal Number | Binary Code | Gray Code |

|----------------|-------------|-----------|

| 0              | 0000        | 0000      |

| 1              | 0001        | 0001      |

| 2              | 0010        | 0011      |

| 3              | 0011        | 0010      |

| 4              | 0100        | 0110      |

| 5              | 0101        | 0111      |

| 6              | 0110        | 0101      |

| 7              | 0111        | 0100      |

| 8              | 1000        | 1100      |

| 9              | 1001        | 1101      |

| 10             | 1010        | 1111      |

| 11 | 1011 | 1110 |

|----|------|------|

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

#### **Error Detecting and Correction Codes**

- Error detecting codes: When data is transmitted from one point to another, like in wireless transmission, or it is just stored, like in hard disks and there are chances that data may get corrupted. To detect these data errors, we use special codes, which are error detection codes.

- Error correcting code: Error-correcting codes not only detect errors, but also correct them. This is used normally in Satellite communication, where turn-around delay is very high as is the probability of data getting corrupt.

- Hamming codes: Hamming code adds a minimum number of bits to the data transmitted in a noisy channel, to be able to correct every possible one-bit error. It can detect (not correct) two-bit errors and cannot distinguish between 1-bit and 2-bits inconsistencies. It can't in general detect 3(or more)-bits errors.

- Parity codes: A parity bit is an extra bit included with a message to make the total number of 1's either even or odd. In parity codes, every data byte, or nibble (according to how user wants to use it) is checked if they have even number of ones or even number of zeros. Based on this information an additional bit is appended to the original data. Thus if we consider 8-bit data, adding the parity bit will make it 9 bit long.

At the receiver side, once again parity is calculated and matched with the received parity (bit 9), and if they match, data is ok, otherwise data is corrupt.

#### Two types of parity

- 1) Even parity: Checks if there is an even number of ones; if so, parity bit is zero. When the number of one's is odd then parity bit is set to 1.

- 2) Odd Parity: Checks if there is an odd number of ones; if so, parity bit is zero. When the number of one's is even then parity bit is set to 1.

#### **Alphanumeric codes:**

The binary codes that can be used to represent the letters of the alphabet, numbers and mathematical symbols, punctuation marks are known as alphanumeric codes or character codes. These codes enable us to interface the input-output devices like the keyboard, printers, video displays with the computer.

• ASCII codes: Codes to handle alphabetic and numeric information, special symbols,

punctuation marks, and control characters. ASCII (American Standard Code for Information Interchange) is the best known. Unicode – a 16-bit coding system provides for foreign languages, mathematical symbols, geometrical shapes, dingbats, etc. It has become a world standard alphanumeric code for microcomputers and computers. It is a 7-bit code representing 128 different characters. These characters represe upper case letters (A to Z), 26 lowercase letters (a to z), 10 numbers (0 to 9), 33 special characters and symbols and 33 control characters.

• **EBCDIC codes**: EBCDIC stands for Extended Binary Coded Decimal Interchange. It is mainly used with large computer systems like mainframes. EBCDIC is an 8-bit code and thus accommodates up to 256 characters. An EBCDIC code is divided into two portions: 4 zone bits (on the left) and 4 numeric bits (on the right).

Example 1: Give the binary, BCD, Excess-3, gray code representations of numbers:5,8,14.

| <b>Decimal Number</b> | Binary code | BCD code  | Excess-3 code | Gray code |

|-----------------------|-------------|-----------|---------------|-----------|

| 5                     | 0101        | 0101      | 1000          | 0111      |

| 8                     | 1000        | 1000      | 1011          | 1100      |

| 14                    | 1110        | 0001 0100 | 0100 0111     | 1001      |

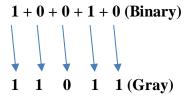

Example 2: Binary To Gray Code Conversion

Example 3: Gray Code To Binary Code Conversion

#### 1.6 Code Converters:

Code to another code of binary code. The following are some of the most commonly used code converters:

- Binary-to-Gray code

- Gray-to-Binary code

- BCD-to-Excess-3

- Excess-3-to-BCD

- Binary-to-BCD

- BCD-to-binary

- Gray-to-BCD

- BCD-to-Gray

- 8 4 -2 -1 to BCD converter

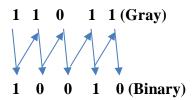

# **Binary to Gray Converters:**

The gray code is often used in digital systems because it has the advantage that only one bitin the numerical representation changes between successive numbers. The truth table for the binary-to-gray code converter is shown below,

Truth table

|         | Binary code |                       |                       |                  | Gray code      |                |    |       |  |

|---------|-------------|-----------------------|-----------------------|------------------|----------------|----------------|----|-------|--|

| Decimal | В3          | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | $\mathbf{B}_{0}$ | G <sub>3</sub> | G <sub>2</sub> | G1 | $G_0$ |  |

| 0       | 0           | 0                     | 0                     | 0                | 0              | 0              | 0  | 0     |  |

| 1       | 0           | 0                     | 0                     | 1                | 0              | 0              | 0  | 1     |  |

| 2       | 0           | 0                     | 1                     | 0                | 0              | 0              | 1  | 1     |  |

| 3       | 0           | 0                     | 1                     | 1                | 0              | 0              | 1  | 0     |  |

| 4       | 0           | 1                     | 0                     | 0                | 0              | 1              | 1  | 0     |  |

| 5       | 0           | 1                     | 0                     | 1                | 0              | 1              | 1  | 1     |  |

| 6       | 0           | 1                     | 1                     | 0                | 0              | 1              | 0  | 1     |  |

| 7       | 0           | 1                     | 1                     | 1                | 0              | 1              | 0  | 0     |  |

| 8       | 1           | 0                     | 0                     | 0                | 1              | 1              | 0  | 0     |  |

| 9       | 1           | 0                     | 0                     | 1                | 1              | 1              | 0  | 1     |  |

| 10      | 1           | 0                     | 1                     | 0                | 1              | 1              | 1  | 1     |  |

| 11      | 1           | 0                     | 1                     | 1                | 1              | 1              | 1  | 0     |  |

| 12      | 1           | 1                     | 0                     | 0                | 1              | 0              | 1  | 0     |  |

| 13      | 1           | 1                     | 0                     | 1                | 1              | 0              | 1  | 1     |  |

| 14      | 1           | 1                     | 1                     | 0                | 1              | 0              | 0  | 1     |  |

| 15      | 1           | 1                     | 1                     | 1                | 1              | 0              | 0  | 0     |  |

# K-map simplification:

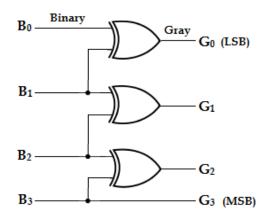

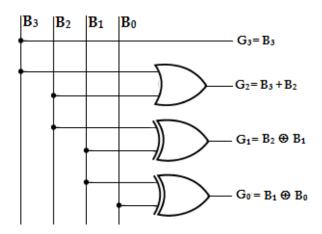

Now, the above expressions can be implemented using EX-OR gates as,

# Logic Diagram:

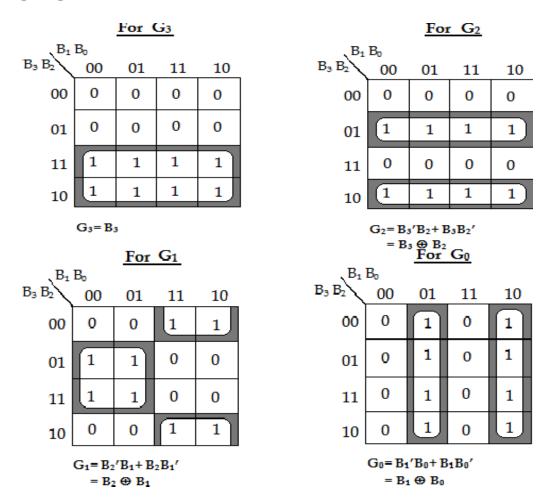

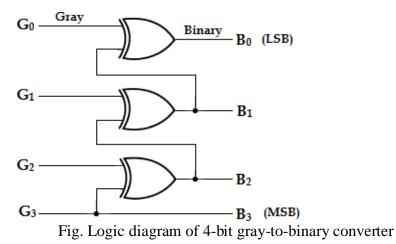

# **Gray to Binary Converters:**

The truth table for the gray-to-binary code converter is shown below,

# Truth table:

| Gray code      |       |       |       | Binary code           |                |                       |                |  |

|----------------|-------|-------|-------|-----------------------|----------------|-----------------------|----------------|--|

| G <sub>3</sub> | $G_2$ | $G_1$ | $G_0$ | <b>B</b> <sub>3</sub> | $\mathbf{B}_2$ | <b>B</b> <sub>1</sub> | $\mathbf{B}_0$ |  |

| 0              | 0     | 0     | 0     | 0                     | 0              | 0                     | 0              |  |

| 0              | 0     | 0     | 1     | 0                     | 0              | 0                     | 1              |  |

| 0              | 0     | 1     | 0     | 0                     | 0              | 1                     | 1              |  |

| 0              | 0     | 1     | 1     | 0                     | 0              | 1                     | 0              |  |

| 0              | 1     | 0     | 0     | 0                     | 1              | 1                     | 1              |  |

| 0              | 1     | 0     | 1     | 0                     | 1              | 1                     | 0              |  |

| 0              | 1     | 1     | 0     | 0                     | 1              | 0                     | 0              |  |

| 0              | 1     | 1     | 1     | 0                     | 1              | 0                     | 1              |  |

| 1              | 0     | 0     | 0     | 1                     | 1              | 1                     | 1              |  |

| 1              | 0     | 0     | 1     | 1                     | 1              | 1                     | 0              |  |

| 1              | 0     | 1     | 0     | 1                     | 1              | 0                     | 0              |  |

| 1              | 0     | 1     | 1     | 1                     | 1              | 0                     | 1              |  |

| 1              | 1     | 0     | 0     | 1                     | 0              | 0                     | 0              |  |

| 1              | 1     | 0     | 1     | 1                     | 0              | 0                     | 1              |  |

| 1              | 1     | 1     | 0     | 1                     | 0              | 1                     | 1              |  |

| 1              | 1     | 1     | 1     | 1                     | 0              | 1                     | 0              |  |

From the truth table, the logic expression for the binary code outputs can be written as,

$G_3 = \sum m (8, 9, 10, 11, 12, 13, 14, 15)$

$G_2 = \sum m (4, 5, 6, 7, 8, 9, 10, 11)$

$G_1 = \sum m (2, 3, 4, 5, 8, 9, 14, 15)$

$G_0 = \sum m (1, 2, 4, 7, 8, 11, 13, 14)$

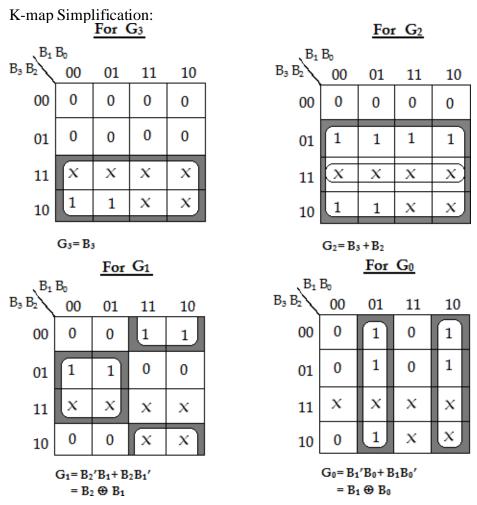

K-map Simplification:

From the above K-map,

$$\begin{split} \mathbf{B}_3 &= \mathbf{G}_3 \\ \mathbf{B}_2 &= \mathbf{G}_3' \mathbf{G}_2 + \mathbf{G}_3 \mathbf{G}_2' \\ \mathbf{B}_2 &= \mathbf{G}_3 \oplus \mathbf{G}_2 \\ \mathbf{B}_1 &= \mathbf{G}_3' \mathbf{G}_2' \mathbf{G}_1 + \mathbf{G}_3' \mathbf{G}_2 \mathbf{G}_1' + \mathbf{G}_3 \mathbf{G}_2 \mathbf{G}_1 + \mathbf{G}_3 \mathbf{G}_2' \mathbf{G}_1' \\ &= \mathbf{G}_3' \left( \mathbf{G}_2' \mathbf{G}_1 + \mathbf{G}_2 \mathbf{G}_1' \right) + \mathbf{G}_3 \left( \mathbf{G}_2 \mathbf{G}_1 + \mathbf{G}_2' \mathbf{G}_1' \right) \\ &= \mathbf{G}_3' \left( \mathbf{G}_2 \oplus \mathbf{G}_1 \right) + \mathbf{G}_3 \left( \mathbf{G}_2 \oplus \mathbf{G}_1 \right)' \\ &= \mathbf{G}_3' \left( \mathbf{G}_2 \oplus \mathbf{G}_1 \right) + \mathbf{G}_3 \left( \mathbf{G}_2 \oplus \mathbf{G}_1 \right)' \\ &= \mathbf{G}_3' \mathbf{G}_2' \left( \mathbf{G}_1' \mathbf{G}_0 + \mathbf{G}_3' \mathbf{G}_2 \mathbf{G}_1 \mathbf{G}_0' + \mathbf{G}_3 \mathbf{G}_2 \mathbf{G}_1 \mathbf{G}_0' + \mathbf{G}_3' \mathbf{G}_2 \mathbf{G}_1' \mathbf{G}_0' + \mathbf{G}_3' \mathbf{G}_2' \mathbf{G}_1' \mathbf{G}_0' + \mathbf{G}_3' \mathbf{G}_2' \mathbf{G}_1' \mathbf{G}_0' + \mathbf{G}_3' \mathbf{G}_2' \mathbf{G}_1' \mathbf{G}_0' + \mathbf{G}_1' \mathbf{G}_0' \left( \mathbf{G}_3' \mathbf{G}_2 + \mathbf{G}_3 \mathbf{G}_2' \right) + \mathbf{G}_1' \mathbf{G}_0' \left( \mathbf{G}_3' \mathbf{G}_2 + \mathbf{G}_3 \mathbf{G}_2' \right) + \mathbf{G}_1' \mathbf{G}_0' \left( \mathbf{G}_3' \mathbf{G}_2 + \mathbf{G}_3 \mathbf{G}_2' \right) + \mathbf{G}_1' \mathbf{G}_0' \left( \mathbf{G}_3' \mathbf{G}_2 + \mathbf{G}_3 \mathbf{G}_2' \right) + \mathbf{G}_1' \mathbf{G}_0' \left( \mathbf{G}_2 \oplus \mathbf{G}_3 \right) + \mathbf{G}_1' \mathbf{G}_0' \left( \mathbf{G}_1' \mathbf{G}_1'$$

Now, the above expressions can be implemented using EX-OR gates as,

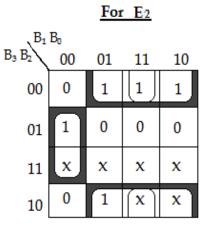

#### **BCD** –to-Excess-3 Converters:

Excess-3 is a modified form of a BCD number. The excess-3 code can be derived from the natural BCD code by adding 3 to each coded number. For example, decimal 12 can be represented in BCD as 0001 0010. Now adding 3 to each digitive get excess-3 code as 0100 0101 (12 in decimal). With this information the truth table for BCD to Excess-3 code converter can be determined as,

Truth Table

|         | BCD code              |                |                       |                | Excess-3 code  |                |                |                |  |

|---------|-----------------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|--|

| Decimal | <b>B</b> <sub>3</sub> | $\mathbf{B}_2$ | <b>B</b> <sub>1</sub> | $\mathbf{B_0}$ | E <sub>3</sub> | $\mathbf{E}_2$ | $\mathbf{E_1}$ | $\mathbf{E_0}$ |  |

| 0       | 0                     | 0              | 0                     | 0              | 0              | 0              | 1              | 1              |  |

| 1       | 0                     | 0              | 0                     | 1              | 0              | 1              | 0              | 0              |  |

| 2       | 0                     | 0              | 1                     | 0              | 0              | 1              | 0              | 1              |  |

| 3       | 0                     | 0              | 1                     | 1              | 0              | 1              | 1              | 0              |  |

| 4       | 0                     | 1              | 0                     | 0              | 0              | 1              | 1              | 1              |  |

| 5       | 0                     | 1              | 0                     | 1              | 1              | 0              | 0              | 0              |  |

| 6       | 0                     | 1              | 1                     | 0              | 1              | 0              | 0              | 1              |  |

| 7       | 0                     | 1              | 1                     | 1              | 1              | 0              | 1              | 0              |  |

| 8       | 1                     | 0              | 0                     | 0              | 1              | 0              | 1              | 1              |  |

| 9       | 1                     | 0              | 0                     | 1              | 1              | 1              | 0              | 0              |  |

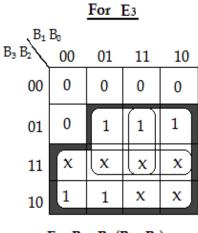

From the truth table, the logic expression for the Excess-3 code outputs can be written as,

E3=

$$\sum$$

m (5, 6, 7, 8, 9) +  $\sum$ d (10, 11, 12, 13, 14, 15)

$$E_2 = \sum m (1, 2, 3, 4, 9) + \sum d(10, 11, 12, 13, 14, 15)$$

$$E_1 = \sum m (0, 3, 4, 7, 8) + \sum d(10, 11, 12, 13, 14, 15)$$

$$E_0 = \sum m (0, 2, 4, 6, 8) + \sum d(10, 11, 12, 13, 14, 15)$$

# K-map Simplification

$$E_3 = B_3 + B_2 (B_0 + B_1)$$

$$E_2 = B_2 B_1' B_0' + B_2' (B_0 + B_1)$$

|                                             | For E1   |    |    |        |  |  |  |  |  |

|---------------------------------------------|----------|----|----|--------|--|--|--|--|--|

| B <sub>3</sub> B <sub>2</sub>               | B₀<br>00 | 01 | 11 | 10     |  |  |  |  |  |

| 00                                          | 1        | 0  | 1  | 0      |  |  |  |  |  |

| 01                                          | 1        | 0  | 1  | 0<br>x |  |  |  |  |  |

| 11                                          | x        | x  | x  |        |  |  |  |  |  |

| 10                                          | 1        | 0  | x  | x      |  |  |  |  |  |

| $E_1 = B_1'B_0' + B_1B_0$ $= B_1 \odot B_0$ |          |    |    |        |  |  |  |  |  |

|                               | For E <sub>0</sub> |    |    |    |  |  |  |  |

|-------------------------------|--------------------|----|----|----|--|--|--|--|

| B <sub>1</sub>                | $B_0$              |    |    |    |  |  |  |  |

| B <sub>3</sub> B <sub>2</sub> | 00                 | 01 | 11 | 10 |  |  |  |  |

| 00                            | 1                  | 0  | 0  | 1  |  |  |  |  |

| 01                            | 1                  | 0  | 0  | 1  |  |  |  |  |

| 11                            | x                  | x  | x  | x  |  |  |  |  |

| 10                            | 1                  | 0  | x  | x  |  |  |  |  |

| 1                             | $E_0 = B_0$        | ,  |    |    |  |  |  |  |

# **Logic Diagram:**

# BCD Code

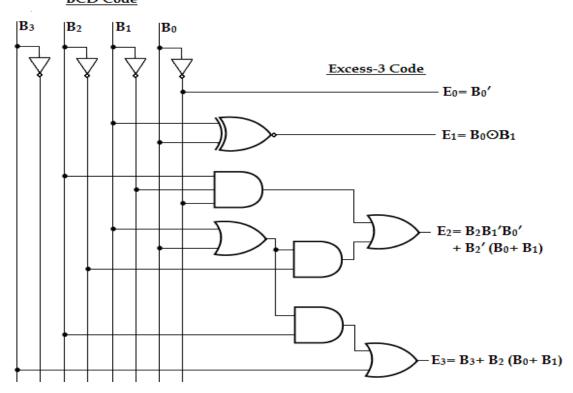

**Excess-3 to BCD Converter: Truth table:**

| Decimal  |                | Excess-3 code  |                |                |                       | BCD code       |                |                |  |

|----------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|----------------|--|

| Deciliai | $\mathbf{E}_3$ | $\mathbf{E}_2$ | $\mathbf{E_1}$ | $\mathbf{E_0}$ | <b>B</b> <sub>3</sub> | $\mathbf{B}_2$ | $\mathbf{B}_1$ | $\mathbf{B}_0$ |  |

| 3        | 0              | 0              | 1              | 1              | 0                     | 0              | 0              | 0              |  |

| 4        | 0              | 1              | 0              | 0              | 0                     | 0              | 0              | 1              |  |

| 5        | 0              | 1              | 0              | 1              | 0                     | 0              | 1              | 0              |  |

| 6        | 0              | 1              | 1              | 0              | 0                     | 0              | 1              | 1              |  |

| 7        | 0              | 1              | 1              | 1              | 0                     | 1              | 0              | 0              |  |

| 8        | 1              | 0              | 0              | 0              | 0                     | 1              | 0              | 1              |  |

| 9        | 1              | 0              | 0              | 1              | 0                     | 1              | 1              | 0              |  |

| 10       | 1              | 0              | 1              | 0              | 0                     | 1              | 1              | 1              |  |

| 11       | 1              | 0              | 1              | 1              | 1                     | 0              | 0              | 0              |  |

| 12       | 1              | 1              | 0              | 0              | 1                     | 0              | 0              | 1              |  |

From the truth table, the logic expression for the Excess-3 code outputs can be written as,

$$B_3 = \sum m (11, 12) + \sum d (0, 1, 2, 13, 14, 15)$$

$$B_2 = \sum m (7, 8, 9, 10) + \sum d(0, 1, 2, 13, 14, 15)$$

$$B_1 = \sum m (5, 6, 9, 10) + \sum d(0, 1, 2, 13, 14, 15)$$

$$B_0 = \sum m (4, 6, 8, 10, 12) + \sum d (0, 1, 2, 13, 14, 15)$$

# K-map Simplification

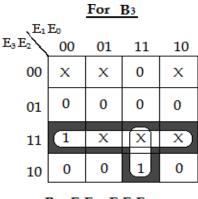

$$B_3 = E_3 E_2 + E_3 E_1 E_0$$

$B_2 = E_2' E_1' + E_2 E_1 E_0 + E_3 E_1 E_0'$

For B<sub>0</sub>

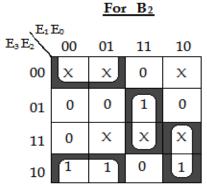

Now, the above expressions the logic diagram can be implemented as,

|                               | For B <sub>1</sub> |    |    |    |  |  |  |  |

|-------------------------------|--------------------|----|----|----|--|--|--|--|

| $E_1$                         | $E_0$              |    |    |    |  |  |  |  |

| E <sub>3</sub> E <sub>2</sub> | 00                 | 01 | 11 | 10 |  |  |  |  |

| 00                            | x                  | X  | 0  | X  |  |  |  |  |

| 01                            | 0                  | 1  | 0  | 1  |  |  |  |  |

| 11                            | 0                  | x  | х  | х  |  |  |  |  |

| 10                            | 0                  | 1  | 0  | 1  |  |  |  |  |

|                               |                    |    |    |    |  |  |  |  |

$$B_1 = E_1'E_0 + E_1E_0'$$

$$= E_1 \oplus E_0$$

| E <sub>1</sub>                | $\mathbf{E}_{0}$ |    |    |    |  |  |

|-------------------------------|------------------|----|----|----|--|--|

| E <sub>3</sub> E <sub>2</sub> | 00               | 01 | 11 | 10 |  |  |

| 00                            | X                | х  | 0  | X  |  |  |

| 01                            | 1                | 0  | 0  | 1  |  |  |

| 11                            | 1                | х  | x  | x  |  |  |

| 10                            | 1                | 0  | 0  | 1  |  |  |

|                               |                  |    |    |    |  |  |

$B_0 = E_0'$

# Logic Diagram:

Excess-3 Code

# **BCD** –to-Binary Converters:

The steps involved in the BCD-to-binary conversion process are as follows:

- The value of each bit in the BCD number is represented by a binary equivalent orweight.

- All the binary weights of the bits that are 1's in the BCD are added.

• The result of this addition is the binary equivalent of the BCD number. Two-digit decimal values ranging from 00 to 99 can be represented in BCDby two 4-bit code groups. For example, 19<sub>10</sub> is represented as,

The left-most four-bit group represents 10 and right-most four-bit group represents 9. The binary representation for decimal 19 is 1910 = 110012.

|                | BCD Code              |                |                       |                  |   | Binary |   |   |   |  |

|----------------|-----------------------|----------------|-----------------------|------------------|---|--------|---|---|---|--|

| B <sub>4</sub> | <b>B</b> <sub>3</sub> | B <sub>2</sub> | <b>B</b> <sub>1</sub> | $\mathbf{B}_{0}$ | E | D      | C | В | A |  |

| 0              | 0                     | 0              | 0                     | 0                | 0 | 0      | 0 | 0 | 0 |  |

| 0              | 0                     | 0              | 0                     | 1                | 0 | 0      | 0 | 0 | 1 |  |

| 0              | 0                     | 0              | 1                     | 0                | 0 | 0      | 0 | 1 | 0 |  |

| 0              | 0                     | 0              | 1                     | 1                | 0 | 0      | 0 | 1 | 1 |  |

| 0              | 0                     | 1              | 0                     | 0                | 0 | 0      | 1 | 0 | 0 |  |

| 0              | 0                     | 1              | 0                     | 1                | 0 | 0      | 1 | 0 | 1 |  |

| 0              | 0                     | 1              | 1                     | 0                | 0 | 0      | 1 | 1 | 0 |  |

| 0              | 0                     | 1              | 1                     | 1                | 0 | 0      | 1 | 1 | 1 |  |

| 0              | 1                     | 0              | 0                     | 0                | 0 | 1      | 0 | 0 | 0 |  |

| 0              | 1                     | 0              | 0                     | 1                | 0 | 1      | 0 | 0 | 1 |  |

| 1              | 0                     | 0              | 0                     | 0                | 0 | 1      | 0 | 1 | 0 |  |

| 1              | 0                     | 0              | 0                     | 1                | 0 | 1      | 0 | 1 | 1 |  |

| 1              | 0                     | 0              | 1                     | 0                | 0 | 1      | 1 | 0 | 0 |  |

| 1              | 0                     | 0              | 1                     | 1                | 0 | 1      | 1 | 0 | 1 |  |

| 1              | 0                     | 1              | 0                     | 0                | 0 | 1      | 1 | 1 | 0 |  |

| 1              | 0                     | 1              | 0                     | 1                | 0 | 1      | 1 | 1 | 1 |  |

| 1              | 0                     | 1              | 1                     | 0                | 1 | 0      | 0 | 0 | 0 |  |

| 1              | 0                     | 1              | 1                     | 1                | 1 | 0      | 0 | 0 | 1 |  |

| 1              | 1                     | 0              | 0                     | 0                | 1 | 0      | 0 | 1 | 0 |  |

| 1              | 1                     | 0              | 0                     | 1                | 1 | 0      | 0 | 1 | 1 |  |

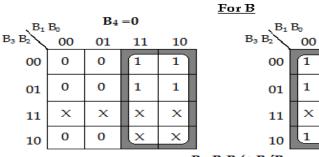

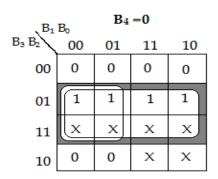

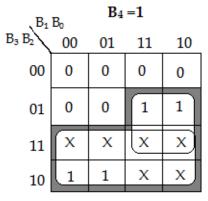

# K-map Simplification:

$B = B_1B_4' + B_1'B_4$  $= B_1 \oplus B_4$

#### For C

| $B_1$ | B <sub>0</sub> | $\mathbf{B}_4$ | =1 |    |  |

|-------|----------------|----------------|----|----|--|

| B₃ B₂ | 00             | 00 01 11       |    | 10 |  |

| 00    | 0              | 0              | 1  | 1  |  |

| 01    | 1              | 1              | 0  | 0  |  |

| 11    | x              | x              | х  | X  |  |

| 10    | 0              | 0              | X  | X  |  |

$B_4 = 1$

11

0

0

х

X

10

0

0

x

X

01

1

1

х

1

$C = B_4'B_2 + B_2B_1' + B_4B_2'B_1$ <u>For D</u>

| $B_1$                         | B <sub>o</sub> |    |    |    |

|-------------------------------|----------------|----|----|----|

| B <sub>3</sub> B <sub>2</sub> | 00             | 01 | 11 | 10 |

| 00                            | 0              | 0  | 0  | 0  |

| 01                            | 0              | 0  | 0  | 0  |

| 11                            | X              | Х  | X  | X  |

| 10                            | 1              | 1  | X  | х  |

| $B_1$ | B <sub>0</sub> | $\mathbf{B_4}$ | =1 |   |

|-------|----------------|----------------|----|---|

| B₃ B₂ | 00             | 01             | 10 |   |

| 00    | 1              | 1              | 1  | 1 |

| 01    | 1              | 1              | 0  | 0 |

| 11    | X              | х              | X  | X |

| 10    | 0              | 0              | х  | x |

$D = B_4'B_3 + B_4B_3'B_2' + B_4B_3'B_1'$

# For E

| $B_1$ | B <sub>0</sub> |       |   |    |

|-------|----------------|-------|---|----|

| B₃ B₂ | 00             | 01 11 |   | 10 |

| 00    | 0              | 0     | 0 | 0  |

| 01    | 0              | 0 0   |   | 0  |

| 11    | X              | X     | X | х  |

| 10    | 0              | 0     | X | Х  |

$E = B_4B_3 + B_4B_2B_1$

From the above K-map,

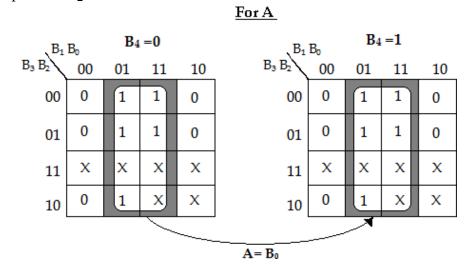

$A=B_0$

$B = B_1B_4' + B1'B4$

$= B_1 Ex-OR B_4$

$C = B_4'B_2 + B_2B_1' + B_4B_2'B_1$

$D = B_4'B3 + B_4B_3'B2' + B4B_3'B1'E = B_4B_3 + B_4B_2B_1$

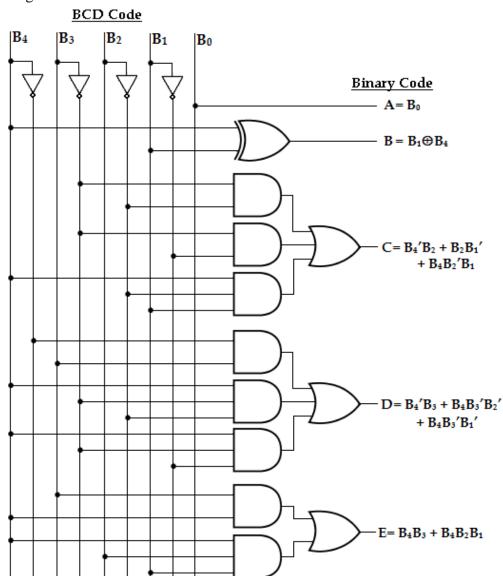

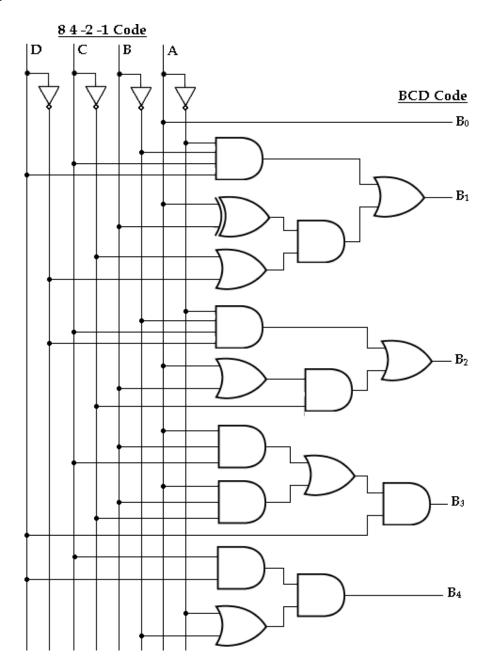

Now, from the above expressions the logic diagram can be implemented as,

# Logic Diagram:

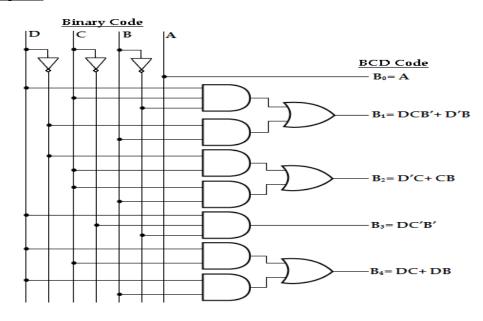

#### **Binary to BCD Converter:**

The truth table for binary to BCD converter can be written as,

Truth Table

| Desimal | Binary Code |   |   |   |                       | BCD Code                                       |   |   |   |  |

|---------|-------------|---|---|---|-----------------------|------------------------------------------------|---|---|---|--|

| Decimal | D           | С | В | A | <b>B</b> <sub>4</sub> | B <sub>4</sub> B <sub>3</sub> B <sub>2</sub> B |   |   |   |  |

| 0       | 0           | 0 | 0 | 0 | 0                     | 0                                              | 0 | 0 | 0 |  |

| 1       | 0           | 0 | 0 | 1 | 0                     | 0                                              | 0 | 0 | 1 |  |

| 2       | 0           | 0 | 1 | 0 | 0                     | 0                                              | 0 | 1 | 0 |  |

| 3       | 0           | 0 | 1 | 1 | 0                     | 0                                              | 0 | 1 | 1 |  |

| 4       | 0           | 1 | 0 | 0 | 0                     | 0                                              | 1 | 0 | 0 |  |

| 5       | 0           | 1 | 0 | 1 | 0                     | 0                                              | 1 | 0 | 1 |  |

| 6       | 0           | 1 | 1 | 0 | 0                     | 0                                              | 1 | 1 | 0 |  |

| 7       | 0           | 1 | 1 | 1 | 0                     | 0                                              | 1 | 1 | 1 |  |

| 8       | 1           | 0 | 0 | 0 | 0                     | 1                                              | 0 | 0 | 0 |  |

| 9       | 1           | 0 | 0 | 1 | 0                     | 1                                              | 0 | 0 | 1 |  |

| 10      | 1           | 0 | 1 | 0 | 1                     | 0                                              | 0 | 0 | 0 |  |

| 11      | 1           | 0 | 1 | 1 | 1                     | 0                                              | 0 | 0 | 1 |  |

| 12      | 1           | 1 | 0 | 0 | 1                     | 0                                              | 0 | 1 | 0 |  |

| 13      | 1           | 1 | 0 | 1 | 1                     | 0                                              | 0 | 1 | 1 |  |

| 14      | 1           | 1 | 1 | 0 | 1                     | 0                                              | 1 | 0 | 0 |  |

| 15      | 1           | 1 | 1 | 1 | 1                     | 0                                              | 1 | 0 | 1 |  |

From the truth table, the logic expression for the BCD code outputs can be written as,

$B_0 = \sum m (1, 3, 5, 7, 9, 11, 13, 15)$

$B_1 = \sum m (2, 3, 6, 7, 12, 13)$

$B_2 = \sum m (4, 5, 6, 7, 14, 15)$

$B_3 = \sum m (8, 9)$

$B_4 = \sum m (10, 11, 12, 13, 14, 15)$

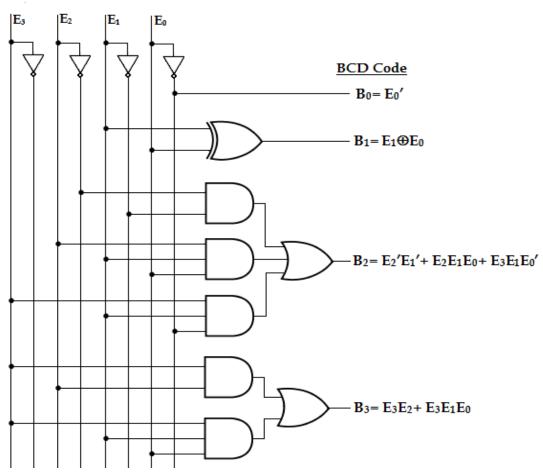

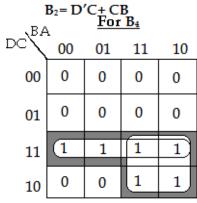

# K-map Simplification:

$B_4 = DC + DB$

From the above K-map, the logical expression can be obtained as,

$B_0 = A$

$$B_4 = DC + DB$$

Now, from the above expressions the logic diagram can be implemented as,

# Logic Diagram:

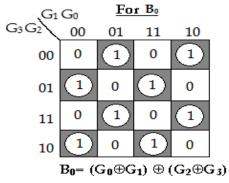

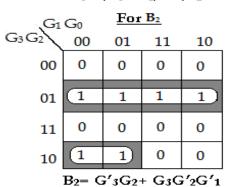

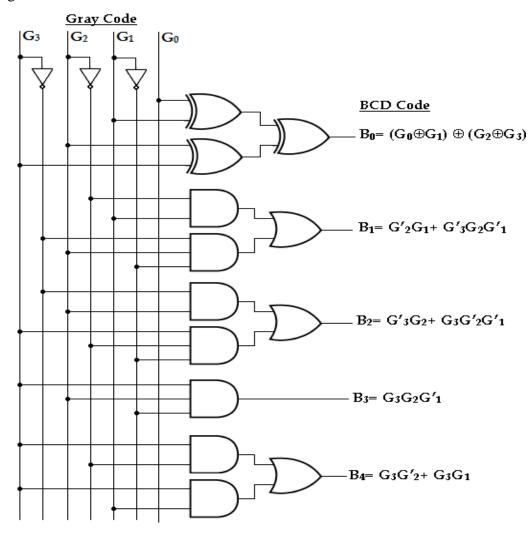

# **Gray to BCD Converter:**

The truth table for gray to BCD converter can be written as,

Truth Table:

| Gray Co        | ode            |       | Trutir | BCD Code   |    |                |                |                |

|----------------|----------------|-------|--------|------------|----|----------------|----------------|----------------|

| G <sub>3</sub> | G <sub>2</sub> | $G_1$ | $G_0$  | <b>B</b> 4 | В3 | $\mathbf{B}_2$ | $\mathbf{B}_1$ | $\mathbf{B_0}$ |

| 0              | 0              | 0     | 0      | 0          | 0  | 0              | 0              | 0              |

| 0              | 0              | 0     | 1      | 0          | 0  | 0              | 0              | 1              |

| 0              | 0              | 1     | 1      | 0          | 0  | 0              | 1              | 0              |

| 0              | 0              | 1     | 0      | 0          | 0  | 0              | 1              | 1              |

| 0              | 1              | 1     | 0      | 0          | 0  | 1              | 0              | 0              |

| 0              | 1              | 1     | 1      | 0          | 0  | 1              | 0              | 1              |

| 0              | 1              | 0     | 1      | 0          | 0  | 1              | 1              | 0              |

| 0              | 1              | 0     | 0      | 0          | 0  | 1              | 1              | 1              |

| 1              | 1              | 0     | 0      | 0          | 1  | 0              | 0              | 0              |

| 1              | 1              | 0     | 1      | 0          | 1  | 0              | 0              | 1              |

| 1              | 1              | 1     | 1      | 1          | 0  | 0              | 0              | 0              |

| 1              | 1              | 1     | 0      | 1          | 0  | 0              | 0              | 1              |

| 1              | 0              | 1     | 0      | 1          | 0  | 0              | 1              | 0              |

| 1              | 0              | 1     | 1      | 1          | 0  | 0              | 1              | 1              |

| 1              | 0              | 0     | 1      | 1          | 0  | 1              | 0              | 0              |

| 1              | 0              | 0     | 0      | 1          | 0  | 1              | 0              | 1              |

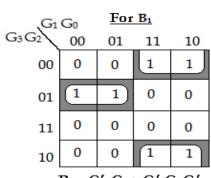

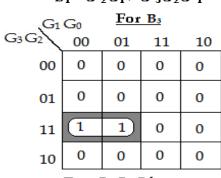

# K-map Simplification:

$B_1 = G'_2G_1 + G'_3G_2G'_1$

$B_3 = G_3G_2G'_1$

| G <sub>3</sub> G <sub>2</sub> G <sub>1</sub> | G <sub>0</sub> | For |    |    |  |

|----------------------------------------------|----------------|-----|----|----|--|

| G3 G2                                        | 00             | 01  | 11 | 10 |  |

| 00                                           | 0              | 0   | 0  | 0  |  |

| 01                                           | 0              | 0   | 0  | 0  |  |

| 11                                           | 0              | 0   | 1  | 1  |  |

| 10                                           | 1              | 1   | 1  | 1  |  |

| $B_4 = G_3G'_2 + G_3G_1$                     |                |     |    |    |  |

From the above K-map, the logical expression can be obtained as,  $B_0 = G'2G_1 + \ G'3G_2G'1 \ B_2 = G'3G_2 + \ G_3G'2G'1 \ B_3 = G_3G_2G'1$  $B_4 = G_3G'_2 + G_3G_1$

Now, from the above expressions the logic diagram can be implemented as,

# Logic Diagram:

# **BCD** to Gray Converter:

The truth table for gray to BCD converter can be written as,

Truth table

| BCD Code (8421) |                       |                       |                | Gray code      |                |                |       |

|-----------------|-----------------------|-----------------------|----------------|----------------|----------------|----------------|-------|

| В3              | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | $\mathbf{B}_0$ | G <sub>3</sub> | G <sub>2</sub> | G <sub>1</sub> | $G_0$ |

| 0               | 0                     | 0                     | 0              | 0              | 0              | 0              | 0     |

| 0               | 0                     | 0                     | 1              | 0              | 0              | 0              | 1     |

| 0               | 0                     | 1                     | 0              | 0              | 0              | 1              | 1     |

| 0               | 0                     | 1                     | 1              | 0              | 0              | 1              | 0     |

| 0               | 1                     | 0                     | 0              | 0              | 1              | 1              | 0     |

| 0               | 1                     | 0                     | 1              | 0              | 1              | 1              | 1     |

| 0               | 1                     | 1                     | 0              | 0              | 1              | 0              | 1     |

| 0               | 1                     | 1                     | 1              | 0              | 1              | 0              | 0     |

| 1               | 0                     | 0                     | 0              | 1              | 1              | 0              | 0     |

| 1               | 0                     | 0                     | 1              | 1              | 1              | 0              | 1     |

Now, from the above expressions the logic diagram can be implemented as,

Logic Diagram:

# **84-2-1 to BCD Converter:**

The truth table for 8 4 -2 -1 to BCD converter can be written as,

Truth Table

| Gray Code |   |   |   | BCD Code              |                       |                |                       |                |

|-----------|---|---|---|-----------------------|-----------------------|----------------|-----------------------|----------------|

| D         | C | В | A | <b>B</b> <sub>4</sub> | <b>B</b> <sub>3</sub> | $\mathbf{B}_2$ | <b>B</b> <sub>1</sub> | $\mathbf{B}_0$ |

| 0         | 0 | 0 | 0 | 0                     | 0                     | 0              | 0                     | 0              |

| 0         | 1 | 1 | 1 | 0                     | 0                     | 0              | 0                     | 1              |

| 0         | 1 | 1 | 0 | 0                     | 0                     | 0              | 1                     | 0              |

| 0         | 1 | 0 | 1 | 0                     | 0                     | 0              | 1                     | 1              |

| 0         | 1 | 0 | 0 | 0                     | 0                     | 1              | 0                     | 0              |

| 1         | 0 | 1 | 1 | 0                     | 0                     | 1              | 0                     | 1              |

| 1         | 0 | 1 | 0 | 0                     | 0                     | 1              | 1                     | 0              |

| 1         | 0 | 0 | 1 | 0                     | 0                     | 1              | 1                     | 1              |

| 1         | 0 | 0 | 0 | 0                     | 1                     | 0              | 0                     | 0              |

| 1         | 1 | 1 | 1 | 0                     | 1                     | 0              | 0                     | 1              |

| 1         | 1 | 1 | 0 | 1                     | 0                     | 0              | 0                     | 0              |

| 1         | 1 | 0 | 1 | 1                     | 0                     | 0              | 0                     | 1              |

| 1         | 1 | 0 | 0 | 1                     | 0                     | 0              | 1                     | 0              |

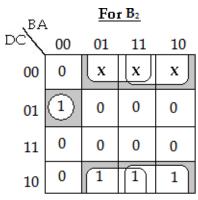

K-map Simplification:

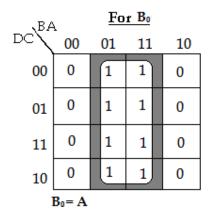

| ,BA                         | For Bo |    |    |    |

|-----------------------------|--------|----|----|----|

| DC                          | 00     | 01 | 11 | 10 |

| 00                          | 0      | x  | x  | x  |

| 01                          | 0      | 1  | 1  | 0  |

| 11                          | 0      | 1  | 1  | 0  |

| 10                          | 0      | 1  | 1  | 0  |

| $\mathbf{B}_0 = \mathbf{A}$ |        |    |    |    |

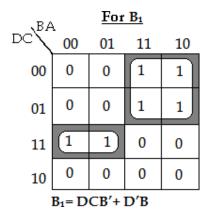

| BA | For B <sub>1</sub> |    |    |     |

|----|--------------------|----|----|-----|

| DC | 00                 | 01 | 11 | 10  |

| 00 | 0                  | X  | х  | (x) |

| 01 | 0                  | 1  | 0  | 1   |

| 11 | 1                  | 0  | 0  | 0   |

| 10 | 0                  | 1  | 0  | 1   |

$B_1 = DCB'A' + D'B'A + D'BA' + C'B'A + C'BA'$ = A'B'CD+ D'(B'A+BA')+ C'(B'A+BA')

$= A'B'CD + D'(A \oplus B) + C'(A \oplus B)$

$= A'B'CD + (A \oplus B) (C' + D')$

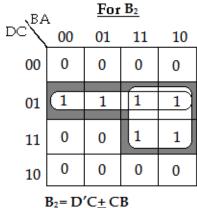

$$B_2 = D'CB'A' + C'A + C'B$$

=  $D'CB'A' + C'(A+B)$

| ВА | L  | <u>F</u> |    |    |

|----|----|----------|----|----|

| DC | 00 | 01       | 11 | 10 |

| 00 | 0  | х        | х  | х  |

| 01 | 0  | 0        | 0  | 0  |

| 11 | 0  | 0        | 1  | 0  |

| 10 | 1  | 0        | 0  | 0  |

$$B_3$$

= ABCD+ A'B'C'D

= D(ABC+ A'B'C')

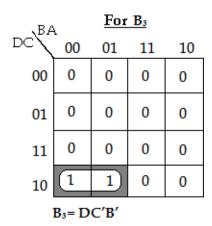

| ,BA   | For B <sub>4</sub> |    |    |    |

|-------|--------------------|----|----|----|

| DC\BA | 00                 | 01 | 11 | 10 |

| 00    | 0                  | х  | x  | х  |

| 01    | 0                  | 0  | 0  | 0  |

| 11    | 1                  | 1  | 0  | 1  |

| 10    | 0                  | 0  | 0  | 0  |

$B_4$ = B'CD+ A'CD = CD( A'+B')

From the above K-map, the logical expression can be obtained as,

$B_0 = A$

$B_1 = A'B'CD + (A Ex-OR B) (C'+D')$

B<sub>2</sub>= D'CB'A'+ C' (A+B)

$B_3 = D (ABC + A'B'C')$

$B_4 = CD (A' + B')$

# Logic Diagram:

#### UNIT 2

# **BOOLEAN ALGEBRA**

In 1854, George Boole, an English mathematician, proposed algebra for symbolically representing problems in logic so that they may be analyzed mathematically. The mathematical systems founded upon the work of Boole are called Boolean algebra in his honor.

# 2.1 Fundamental postulates of Boolean algebra:

The postulates of a mathematical system forms the basic assumption from which it is possibleto deduce the theorems, laws and properties of the system.

The most common postulates used to formulate various structures are

#### Closure:

A set S is closed w.r.t. a binary operator, if for every pair of elements of S, the binary operator specifies a rule for obtaining a unique element of S.The result of each operation with operator (+) or (.) is either 1 or 0 and 1, 0  $\in$ B.

# **Identity element:**

$$e^* x = x * e = x$$

Eg:

$$0+0=0$$

$0+1=1+0=1$

$$0+1=1+0=1$$

a)

$$x + 0 = x$$

$$1 \cdot 1 = 1$$

$1 \cdot 0 = 0 \cdot 1 = 1$

b)

$$x. 1 = x$$

#### **Commutative law:**

A binary operator \* on a set S is said to be commutative if,

$$x * y = y * x$$

Eg:

$$0+1=1+0=1$$

a)

$$x + y = y + x$$

$$0.1 = 1.0 = 0$$

b)

$$x. y= y. x$$

#### **Distributive law:**

If \* and • are two binary operation on a set S, • is said to be distributive over + whenever.

31

$$x \cdot (y+z) = (x \cdot y) + (x \cdot z)$$

Similarly, + is said to be distributive over • whenever,

$$x + (y. z) = (x + y). (x + z)$$

#### Inverse:

a)

$$x + x' = 1$$

, since  $0 + 0' = 0 + 1$  and  $1 + 1' = 1 + 0 = 1$

b) x.

$$x' = 1$$

, since 0 . 0' = 0. 1 and 1. 1' = 1. 0 = 0

#### **Summary**:

Postulates of Boolean algebra:

| POSTULATES                 | (a)             | (b)                       |

|----------------------------|-----------------|---------------------------|

| Postulate 2 (Identity)     | x + 0 = x       | $x \cdot 1 = x$           |

| Postulate 3 (Commutative)  | x + y = y + x   | $x \cdot y = y \cdot x$   |

| Postulate 4 (Distributive) | x (y+z) = xy+xz | x + yz = (x + y). (x + z) |

| Postulate 5 (Inverse)      | x+x'=1          | x. x' = 0                 |

#### 2.2 Basic Theorems:

The theorems, like the postulates are listed in pairs; each relation is the dual of the one paired with it. The postulates are basic axioms of the algebraic structure and need no proof. The theorems must be proven from the postulates. The proofs of the theorems with one variable are presented below. At the right is listed the number of the postulate that justifies each step of the proof.

1a)

$$x + x = x$$

1b)

$$x. x = x$$

$$2) \times .0 = 0$$

3)

$$(x')' = x$$

#### **Absorption Theorem:**

$$x + xy = x$$

$$x + xy = x. \ 1 + xy$$

-------

by postulate 2(b) [  $x. \ 1 = x$  ]

$= x (1 + y)$

-------

$4(a) [ x (y+z) = (xy) + (xz) ]$

$= x (1)$

by theorem  $2(a [x + 1 = x]$

$= x.$

by postulate  $2(a)[x. \ 1 = x]$

$$x. (x+ y) = x$$

$$x. (x + y) = x. x + x. y$$

------  $4(a) [x (y+z) = (xy) + (xz)]$

### 2.3 Properties of Boolean algebra:

### **Commutative property:**

Boolean addition is commutative, given by

$$x + y = y + x$$

According to this property, the order of the OR operation conducted on the variables makesno difference. Boolean algebra is also commutative over multiplication given by,

$$x. y = y. x$$

This means that the order of the AND operation conducted on the variables makes no difference.

#### **Associative property:**

The associative property of addition is given by,

$$A+(B+C) = (A+B) + C$$

The OR operation of several variables results in the same, regardless of the grouping of the variables. The associative law of multiplication is given by,

$$A. (B. C) = (A.B). C$$

It makes no difference in what order the variables are grouped during the AND operation of several variables.

# Distributive property:

The Boolean addition is distributive over Boolean multiplication, given by

$$A+BC = (A+B)(A+C)$$

The Boolean addition is distributive over Boolean addition, given by

A.

$$(B+C) = (A.B)+(A.C)$$

# **Duality:**

It states that every algebraic expression deducible from the postulates of Boolean algebraremains valid if the operators and identity elements are interchanged.

If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

$$x+ x' = 1$$

is x.  $x' = 0$

Duality is a very important property of Boolean algebra.

# **Summary**:

Theorems of Boolean algebra:

|   | THEOREMS           | (a)             | (b)               |

|---|--------------------|-----------------|-------------------|

|   |                    | x + x = x       | $x \cdot x = x$   |

| 1 | Idempotent         | x + 1 = 1       | $x \cdot 0 = 0$   |

| 2 | Involution         | (x')' = x       |                   |

| 2 | Ahaamtian          | x + xy = x      | x (x+y) = x       |

| 3 | Absorption         | x+x'y=x+y       | x. (x'+y) = xy    |

| 4 | Associative        | x+(y+z)=(x+y)+z | x (yz) = (xy) z   |

| 5 | DeMorgan's Theorem | (x+y)'=x'.y'    | (x. y)' = x' + y' |

#### **DeMorgan's Theorems:**

Two theorems that are an important part of Boolean algebra were proposed by DeMorgan. The first theorem states that the complement of a product is equal to the sum of the complements.

$$(AB)' = A' + B'$$

The second theorem states that the complement of a sum is equal to the product of the complements.

$$(A+B)' = A'. B'$$

# **Consensus Theorem:**

In simplification of Boolean expression, an expression of the form **AB+ A'C+ BC**, the term BC is redundant and can be eliminated to form the equivalent expression AB+ A'C. The theorem used for this simplification is known as consensus theorem and is stated as,

$$AB+A'C+BC=AB+A'C$$

The dual form of consensus theorem is stated as,

$$(A+B) (A'+C) (B+C) = (A+B) (A'+C)$$

#### 2.4 Boolean Functions:

Re- arranging, = A' + AB'+ B+ C'

Minimization of Boolean Expressions:

The Boolean expressions can be simplified by applying properties, laws and theorems of Boolean algebra.

Simplify the following Boolean functions to a minimum number of literals:

[A' + AB = A' + B]

[x + xy = x]

= x' + y'z'.

#### 2.5 Complement of A Function:

The complement of a function F is F' and is obtained from an interchange of 0's for 1's and 1's for 0's in the value of F. The complement of a function may be derived algebraically through DeMorgan's theorem.

DeMorgan's theorems for any number of variables resemble in form the two-variable case and can be derived by successive substitutions similar to the method used in the preceding derivation. These theorems can be generalized as –

$$(A+B+C+D+...+F)' = A'B'C'D'...F'$$

$(ABCD...F)' = A'+B'+C'+D'+...+F'.$

Find the complement of the following functions,

1. F = x'yz' + x'y'z

$$F' = (x'yz' + x'y'z)'$$

$$= (x'' + y' + z'') \cdot (x'' + y'' + z')$$

$$= (x + y' + z) \cdot (x + y + z').$$

2.

$$F = (xy + y'z + xz) \cdot x.$$

$$F' = [(xy + y'z + xz) \cdot x]'$$

$$= (xy + y'z + xz)' + x'$$

$$= [(xy)' \cdot (y'z)' \cdot (xz)'] + x'$$

$$= [(x'+y') \cdot (y+z') \cdot (x'+z')] + x'$$

$$= [(x'+y') \cdot (y+z') \cdot (x'+z')] + x'$$

$$= [(x'+y') \cdot (y+z') \cdot (x'+z')] + x'$$

$$= x'x'y + x'z' + x'y'z' + x'yz' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'y'z' + x'yz' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' \cdot (y' + y) + y'z' + x'$$

$$= x'y + x'z' + x'z' \cdot (y' + y) + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z' + y'z' + x'$$

$$= x'y + x'z' + x'z'$$

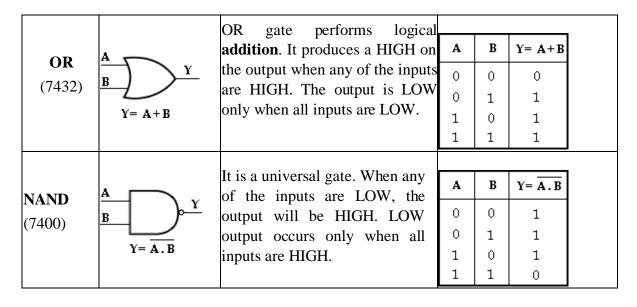

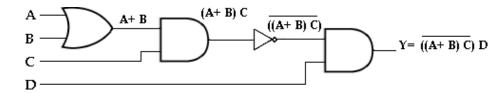

## 2.6 Logic Gates

# 2.6.1 Basic Logic Gates:

Logic gates are electronic circuits that can be used to implement the most elementary logic expressions, also known as Boolean expressions. The logic gate is the most basic building block of combinational logic.

There are three basic logic gates, namely the OR gate, the AND gate and the NOT gate. Other logic gates that are derived from these basic gates are the NAND gate, the NOR gate, the EXCLUSIVE- OR gate and the EXCLUSIVE-NOR gate.

| GATE              | SYMBOL                                                             | OPERATION                                                                                                                                                  | TRU'             | гн т                       | ABLE           |  |

|-------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|----------------|--|

| <b>NOT</b> (7404) | <u>A</u> <u>Y</u> = <u>A</u>                                       | NOT gate (Inversion), produces<br>an inverted output pulse for a<br>given input pulse.                                                                     | <b>A</b> 0 1     | $Y = \overline{A}$ $1$ $0$ | <u> </u>       |  |

| <b>AND</b> (7408) | $ \begin{array}{c c} A \\ \hline B \end{array} $ $ Y = A \cdot B $ | AND gate performs logical <b>multiplication</b> . The output is HIGH only when all the inputs are HIGH. When any of the inputs are low, the output is LOW. | <b>A</b> 0 0 1 1 | B 0 1 0 1 1                | Y= A.B 0 0 0 1 |  |

|         |                                               | It is a surious at a LOW                                  |   |   |                        |  |

|---------|-----------------------------------------------|-----------------------------------------------------------|---|---|------------------------|--|

| NOR     | A ~                                           | It is a universal gate. LOW output occurs when any of its | A | В | $Y = \overline{A + B}$ |  |

| NOK     | $\overline{B}$ $\rightarrow \frac{Y}{A}$      | input is HIGH. When all its                               | 0 | 0 | 1                      |  |

|         |                                               | inputs are LOW, the output is                             | 0 | 1 | 0                      |  |

|         | Y = A + B                                     | HIGH.                                                     | 1 | 0 | 0                      |  |

|         |                                               |                                                           | 1 | 1 | 0                      |  |

|         |                                               |                                                           |   |   |                        |  |

| EX- OR  | A                                             | The output is HIGH only when                              | A | В | Y= <b>A</b> ⊕ <b>B</b> |  |

| LA- OK  | $\overline{\mathbf{B}}$ ) $\mathbf{Y}$        | odd number of inputs is HIGH.                             | 0 | 0 | 0                      |  |

|         |                                               | 1                                                         | 0 | 1 | 1                      |  |

|         | Y= A⊕B                                        |                                                           | 1 | 0 | 1                      |  |

|         |                                               |                                                           | 1 | 1 | 0                      |  |

|         |                                               |                                                           |   |   |                        |  |

| EX- NOR | $\frac{A}{B}$ $\frac{Y}{A}$                   | The output is HIGH only when                              | A | В | Y= A⊙B                 |  |

| EA- NOR |                                               | even number of inputs is HIGH.                            | 0 | 0 | 1                      |  |

|         | $Y = \overline{\mathbf{A} \oplus \mathbf{B}}$ | Or when all inputs are zeros.                             | 0 | 1 | 0                      |  |

|         | (or)                                          |                                                           | 1 | 0 | 0                      |  |

|         | Y= A⊙B                                        |                                                           | 1 | 1 | 1                      |  |

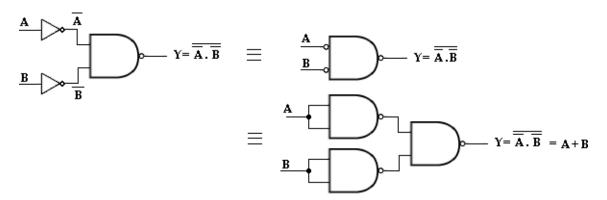

### **2.6.2 UNIVERSAL GATES:**

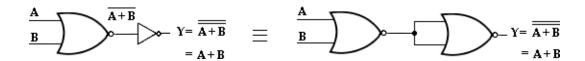

The NAND and NOR gates are known as universal gates, since any logic function can be implemented using NAND or NOR gates. This is illustrated in the following sections.

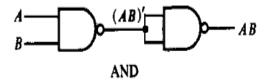

### • NAND Gate:

The NAND gate can be used to generate the NOT function, the AND function, the OR function and the NOR function.

NOT function: By connecting all the inputs together and creating a single common input.

AND function: By simply inverting output of the NAND gate. i.e.,

OR function: Simply inverting inputs of the AND gate . i.e., By bubble at the input of NAND gate indicates inverted input

| A | В | Y= A+B |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

| A | В | $\overline{\mathbf{A}}.\overline{\mathbf{B}}$ | $\overline{\overline{\mathbf{A}}.\overline{\mathbf{B}}}$ |

|---|---|-----------------------------------------------|----------------------------------------------------------|

| 0 | 0 | 1                                             | 0                                                        |

| 0 | 1 | 0                                             | 1                                                        |

| 1 | 0 | 0                                             | 1                                                        |

| 1 | 1 | 0                                             | 1                                                        |

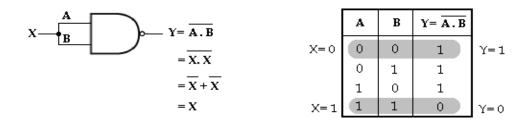

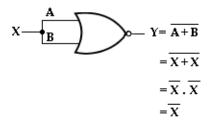

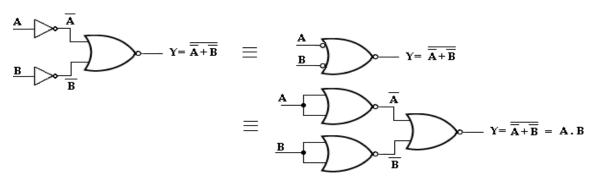

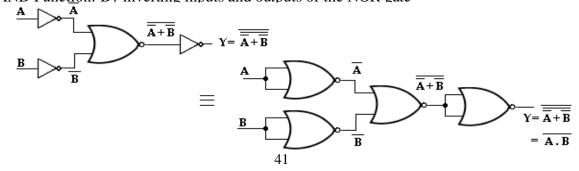

### • NOR Gate:

Similar to NAND gate, the NOR gate is also a universal gate, since it can be used to generatethe NOT, AND, OR and NAND functions.

• NOT function: By connecting all the inputs together and creating a single common input.

$\equiv$

|     | A | В | $Y = \overline{A + B}$ |      |

|-----|---|---|------------------------|------|

| X=0 | 0 | 0 | 1                      | Y= 1 |

|     | 0 | 1 | 0                      |      |

|     | 1 | 0 | 0                      |      |

| X=1 | 1 | 1 | 0                      | Y=0  |

• OR function: By Simply inverting output of the NOR gate.i.e,

| A | В | Y= A+B |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

| A | В | A+B | A+B |

|---|---|-----|-----|

| 0 | 0 | 1   | 0   |

| 0 | 1 | 0   | 1   |

| 1 | 0 | 0   | 1   |

| 1 | 1 | 0   | 1   |

• AND function: By simply inverting inputs of the NOR gate. i.e., Bubble at the input of NOR gate indicates inverted input

$\equiv$

| _ | A | В | $Y = A \cdot B$ |

|---|---|---|-----------------|

|   | 0 | 0 | 0               |

|   | 0 | 1 | 0               |

| : | 1 | 0 | 0               |

|   | 1 | 1 | 1               |

| A | В | $\overline{A} + \overline{B}$ | $\overline{\overline{A} + \overline{B}}$ |

|---|---|-------------------------------|------------------------------------------|

| 0 | 0 | 1                             | 0                                        |

| 0 | 1 | 1                             | 0                                        |

| 1 | 0 | 1                             | 0                                        |

| 1 | 1 | 0                             | 1                                        |

• NAND Function: By inverting inputs and outputs of the NOR gate

| A | В | $Y = \overline{A \cdot B}$ |

|---|---|----------------------------|

| 0 | 0 | 1                          |

| 0 | 1 | 1                          |

| 1 | 0 | 1                          |

| 1 | 1 | 0                          |

| 0         0         1         0         1           0         1         1         0         1           1         0         1         0         1 | A | В | $\overline{A} + \overline{B}$ | $\overline{A} + \overline{B}$ | $\overline{\overline{A} + \overline{B}}$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-------------------------------|-------------------------------|------------------------------------------|

|                                                                                                                                                   | 0 | 0 | 1                             | 0                             | 1                                        |

| 1 0 1 0 1                                                                                                                                         | 0 | 1 | 1                             | 0                             | 1                                        |

|                                                                                                                                                   | 1 | 0 | 1                             | 0                             | 1                                        |

|                                                                                                                                                   | 1 | 1 | 0                             | 1                             | 0                                        |

Conversion of AND/OR/NOT NAND/NOR:

#### <u>to</u>

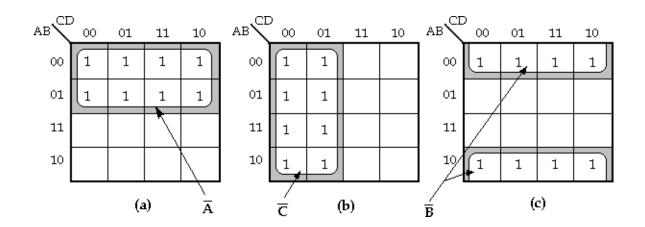

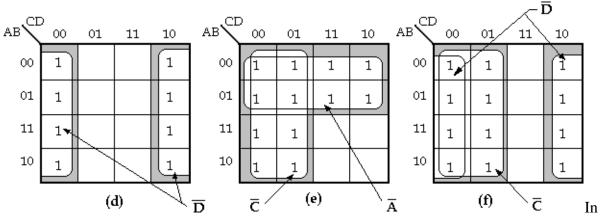

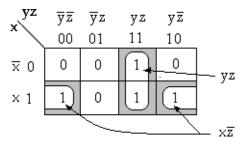

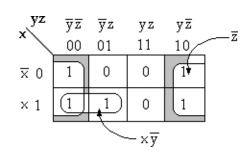

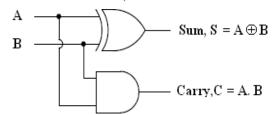

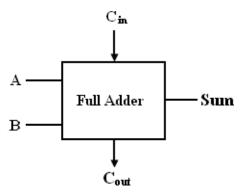

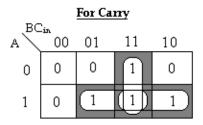

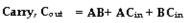

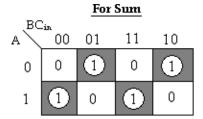

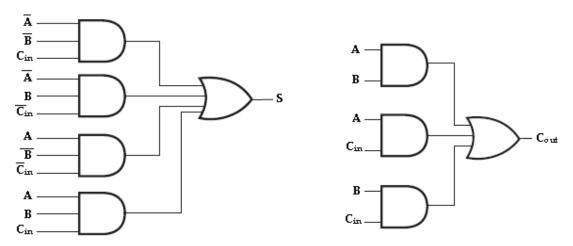

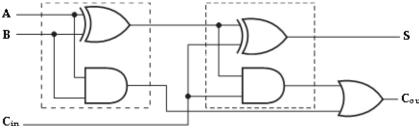

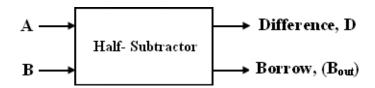

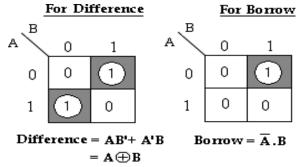

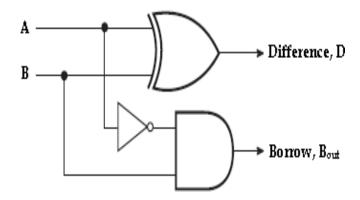

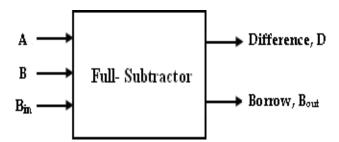

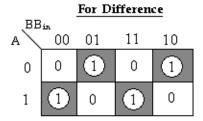

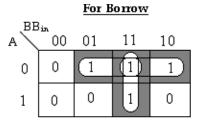

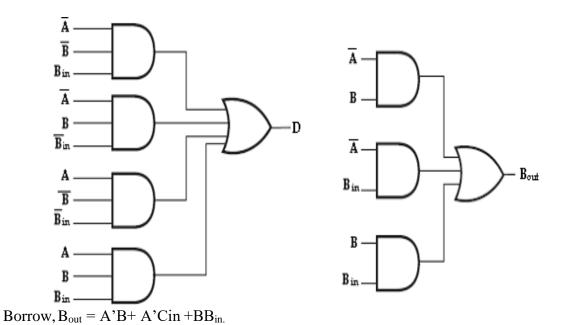

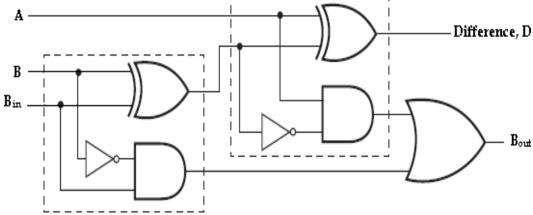

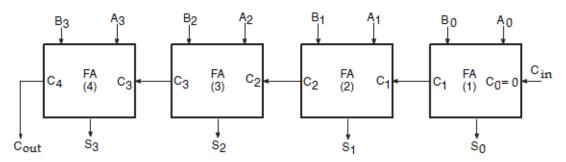

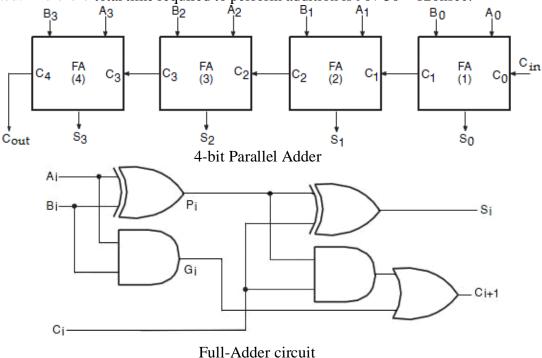

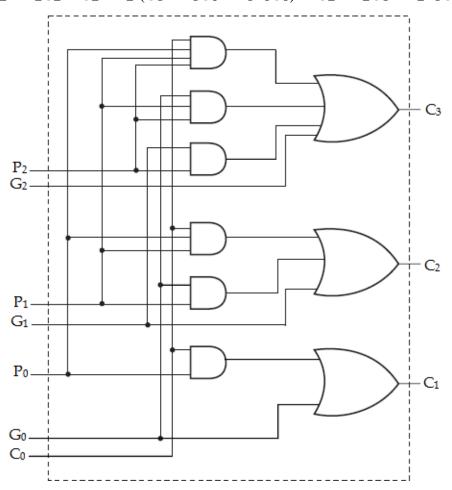

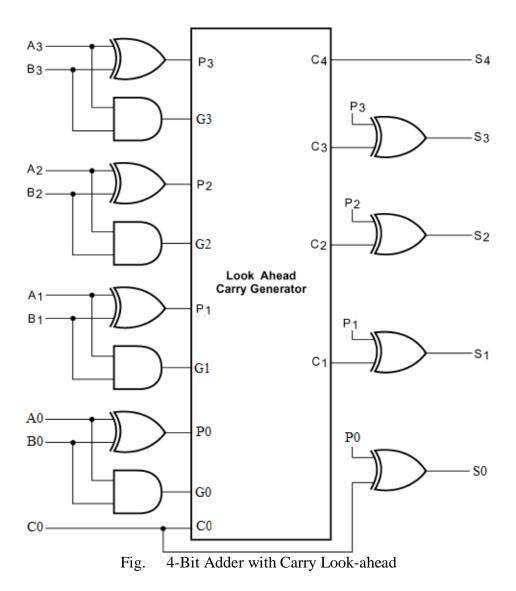

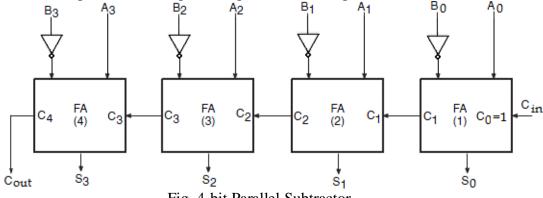

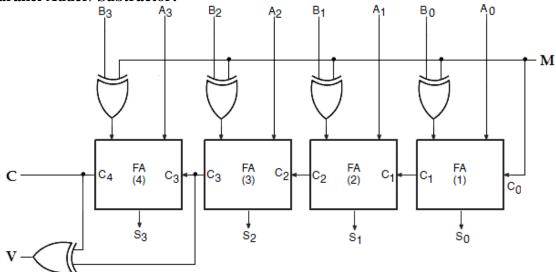

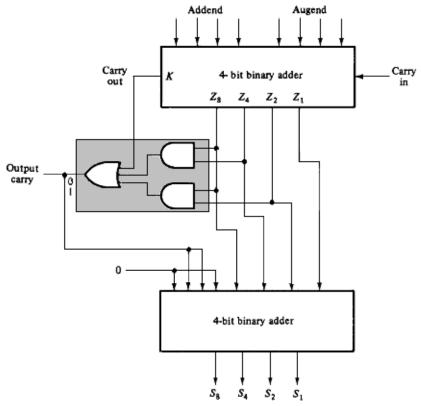

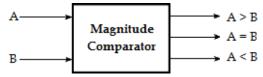

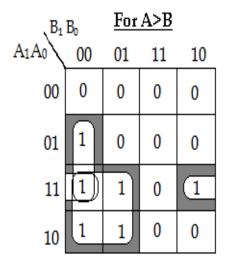

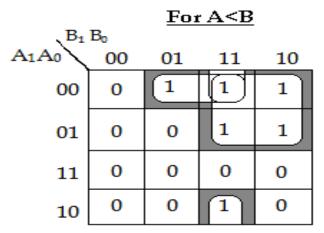

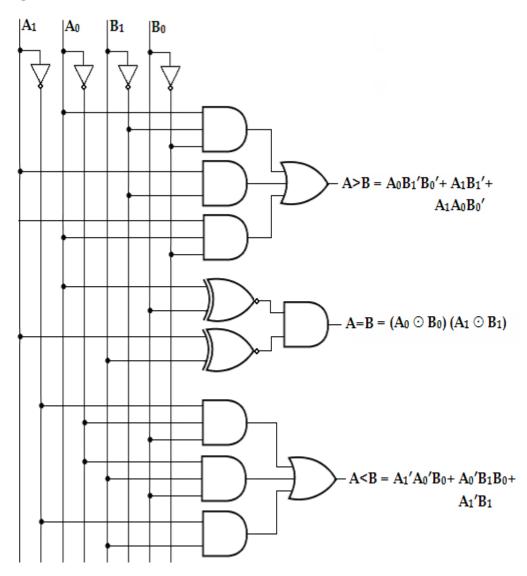

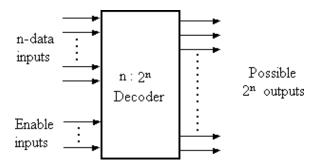

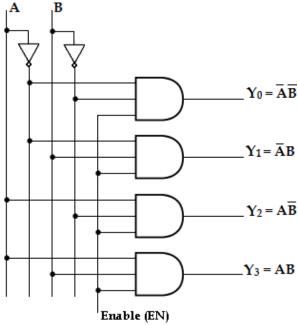

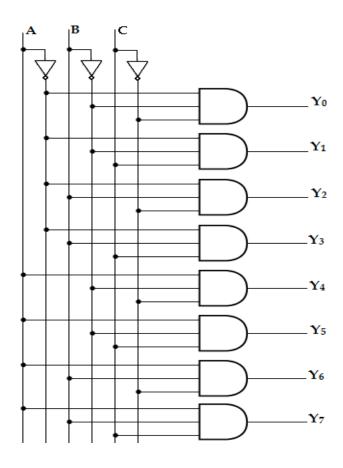

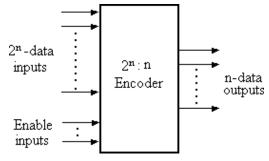

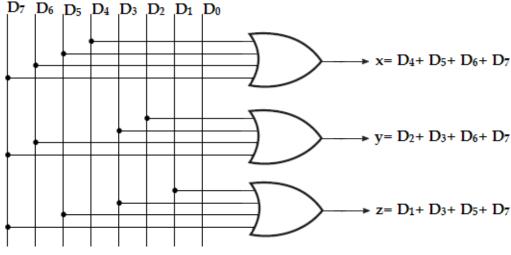

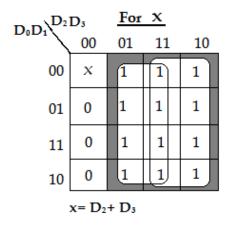

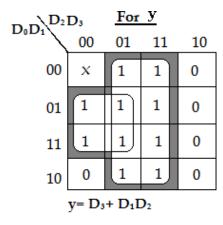

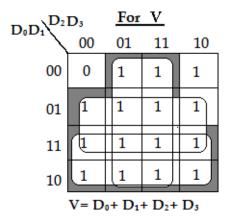

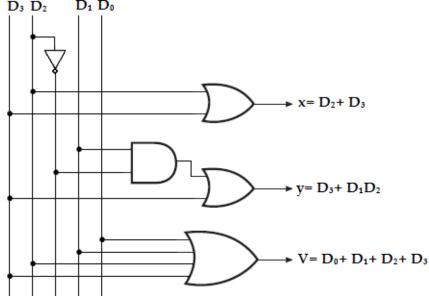

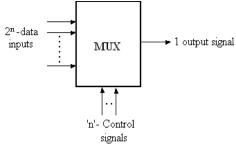

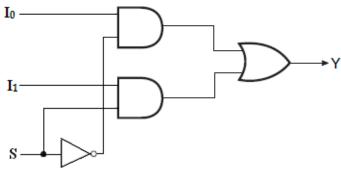

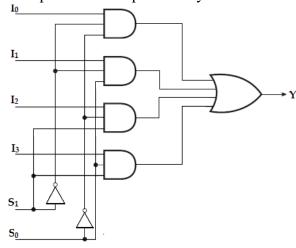

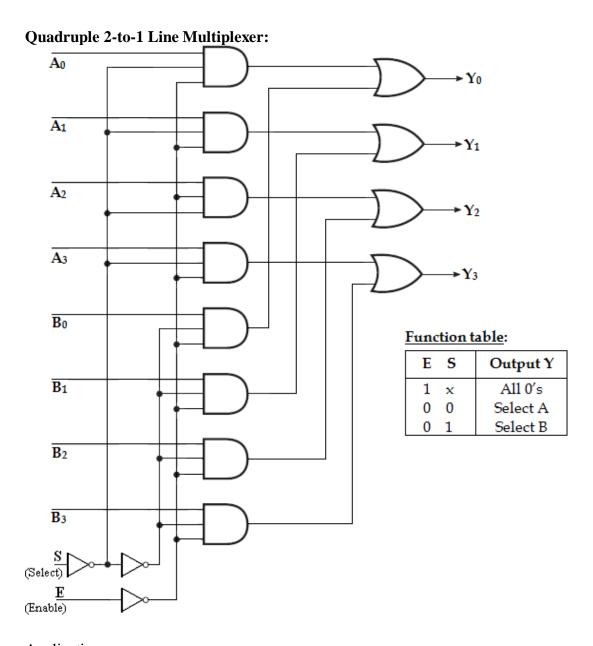

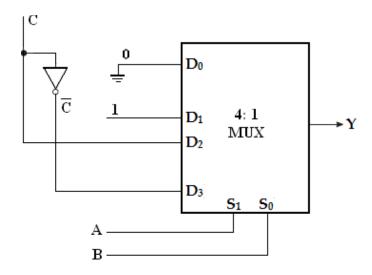

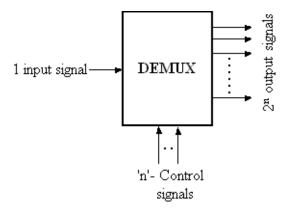

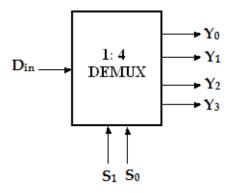

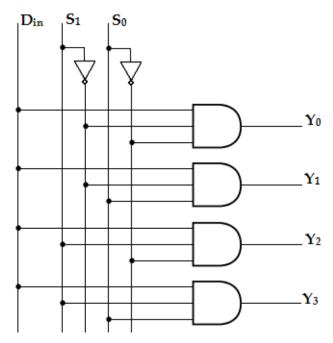

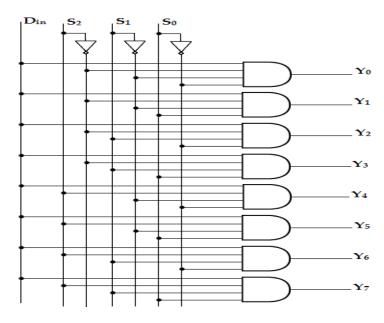

- Draw AND/OR logic.